Image Generated Using 4o

What Is Data Gravity And Why It Matters In Semiconductors

The term “data gravity” originated in cloud computing to describe a simple but powerful phenomenon: as data accumulates in one location, it becomes harder to move, and instead, applications, services, and compute resources are pulled toward it.

In the semiconductor industry, this concept is not just relevant, it is central to understanding many of the collaboration and efficiency challenges teams face today.

Semiconductor development depends on highly distributed toolchains. Design engineers work with EDA tools on secure clusters, test engineers rely on ATE systems, yield analysts process gigabytes of parametric data, and customer telemetry feeds back into field diagnostics.

Consider a few common examples:

- RTL simulation datasets stored on isolated HPC systems, inaccessible to ML workflows hosted in the cloud

- Wafer test logs are locked in proprietary ATE formats or local storage, limiting broader debug visibility

- Yield reports are buried in fab-side data lakes, disconnected from upstream design teams, and are used for troubleshooting quality issues

- Post-silicon debug results that never make it back to architecture teams due to latency, access control, or incompatible environments

Yet all of this breaks down when data cannot move freely across domains or reach the people who need it most. The result is bottlenecks, blind spots, and duplicated effort.

These are not rare cases. They are systemic patterns. As data grows in volume and value, it also becomes more challenging to move, more expensive to duplicate, and more fragmented across silos. That is the gravity at play. And it is reshaping how semiconductor teams operate.

Where Does Data Gravity Arise In Semiconductor Workflows?

To grasp the depth of the data gravity problem in semiconductors, we must examine where data is generated and how it becomes anchored to specific tools, infrastructure, or policies, making it increasingly difficult to access, share, or act upon.

The table below summarizes this:

| Stage | Data Generated | Typical Storage Location | Gravity Consequence |

|---|---|---|---|

| Front-End Design | Netlists, simulation waveforms, coverage metrics | EDA tool environments, NFS file shares | Data stays close to local compute, limiting collaboration and reuse |

| Back-End Verification | Timing reports, power grid checks, IR drop analysis | On-prem verification clusters | Data is fragmented across tools and vendors, slowing full-chip signoff |

| Wafer Test | Shmoo plots, pass/fail maps, binning logs | ATE systems, test floor databases | Debug workflows become localized, isolating valuable test insights |

| Yield and Analytics | Defect trends, parametric distributions, WAT data | Internal data lakes, fab cloud platforms | Insightful data often remains siloed from design or test ML pipelines |

| Field Operations | RMA reports, in-system diagnostics | Secure internal servers or vaults | Feedback to design teams is delayed due to access and compliance gaps |

Data in semiconductor workflows is not inherently immovable, but once it becomes tied to specific infrastructure, proprietary formats, organizational policies, and bandwidth limitations, it starts to resist movement. This gravity effect builds over time, reducing efficiency, limiting visibility, and slowing responsiveness across teams.

The Impact Of Data Gravity On Semiconductor Teams

As semiconductor workflows become more data-intensive, teams across the product lifecycle are finding it increasingly difficult to move, access, and act on critical information. Design, test, yield, and field teams each generate large datasets, but the surrounding infrastructure is often rigid, siloed, and tightly tied to specific tools. This limits collaboration and slows feedback.

For instance, test engineers may detect a recurring fail pattern at wafer sort, but the related data is too large or sensitive to share. As a result, design teams may not see the whole picture until much later. Similarly, AI models for yield or root cause analysis lose effectiveness when training data is scattered across disconnected systems.

Engineers often spend more time locating and preparing data than analyzing it. Redundant storage, manual processes, and disconnected tools reduce productivity and delay time-to-market. Insights remain locked within silos, limiting organizational learning.

In the end, teams are forced to adapt their workflows around where data lives. This reduces agility, slows decisions, and weakens the advantage that integrated data should provide.

Overcoming Data Gravity In Semiconductor

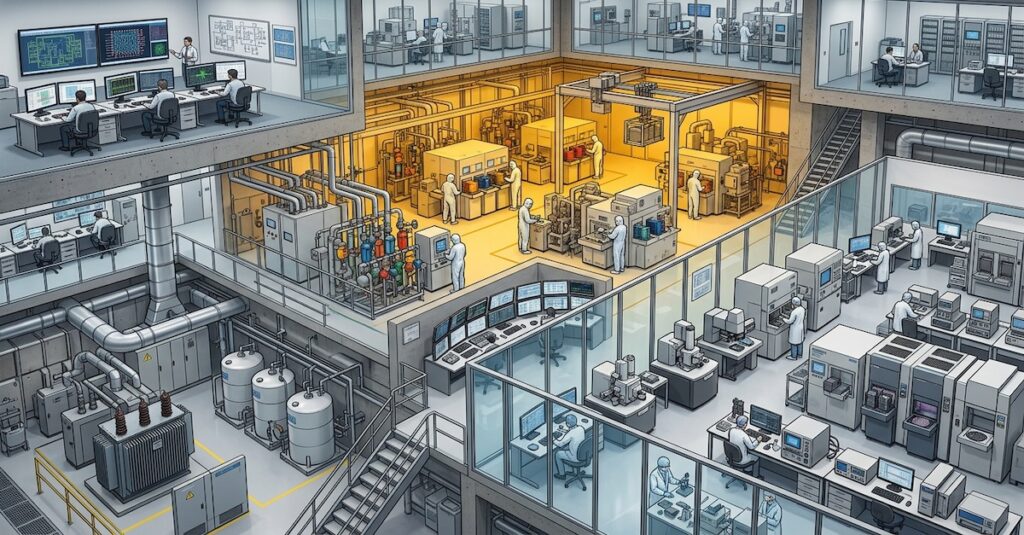

Escaping data gravity starts with rethinking how semiconductor teams design their workflows. Instead of moving large volumes of data through rigid pipelines, organizations should build architectures that enable computation and analysis to occur closer to where data is generated.

Cloud-native, hybrid, and edge-aware systems can support local inference, real-time monitoring, or selective data sharing. Even when whole data movement is not feasible, streaming metadata or feature summaries can preserve value without adding network or compliance burdens.

Broader access can also be achieved through federated data models and standardized interfaces. Many teams work in silos, not by preference, but because incompatible formats, access restrictions, or outdated tools block collaboration.

Aligning on common data schemas, APIs, and secure access frameworks helps reduce duplication and connects teams across design, test, and field operations. Addressing data gravity is not just a technical fix.

It is a strategic step toward faster, wiser, and more integrated semiconductor development.