Image Generated Using 4o

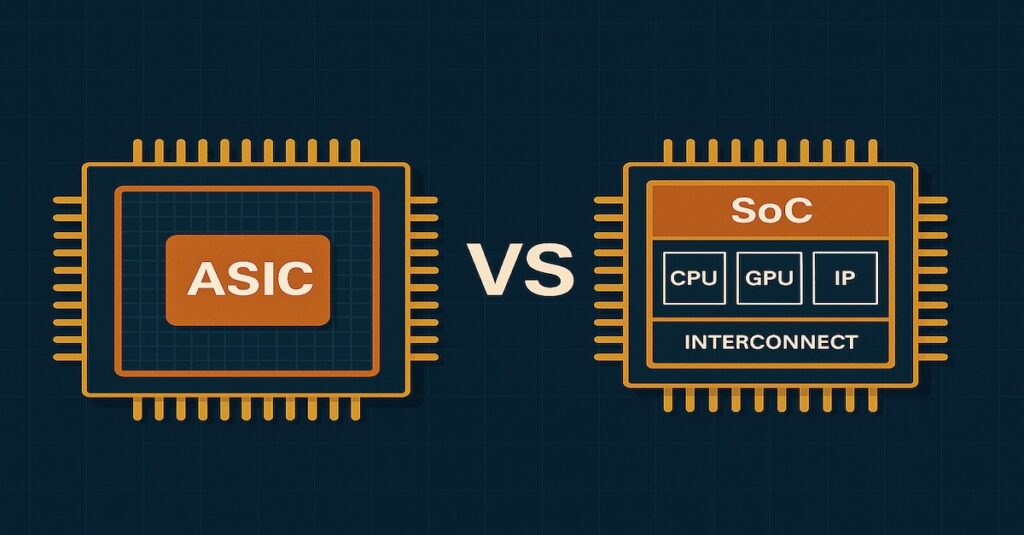

What ASIC And SoC Actually Mean Today

An ASIC was a fixed-function chip logic designed from scratch, optimized for area, power, and speed, and then locked down. It worked particularly well for high-volume products, where every bit of efficiency mattered.

A System-On-A-Chip (SoC) integrates multiple functions, including CPU, memory controllers, accelerators, and I/Os, using pre-verified IP blocks. It reduced design time but gave up some control.

The question is no longer “Is it an ASIC or SoC?” It is:

- How much of it is reused?

- How configurable is it?

- How much control do you have?

- Can team handle the integration and bring it up to speed?

That line is now blurred. Most ASICs use third-party IPs. Some System-On-A-Chip (SoC) devices are heavily customized for specific applications. And hybrids, such as semi-custom SoCs and chiplet-based designs, mix both worlds.

Design Tradeoffs: Cost, Time, And Risk

The core difference between ASIC and SoC design is not technical. It is about tradeoffs. Engineering teams rarely get unlimited time, budget, or people. Every decision shifts pressure to another part of the process, resulting in more integration, extended verification, higher costs, or added schedule risk.

ASICs and SoCs have different profiles in terms of cost structure, development time, silicon risk, and maintainability. These factors are not always apparent at the outset, especially when decision-makers prioritize performance or BOM reduction.

The table below outlines the practical differences most teams encounter:

| Factor | ASIC Design | SoC Design |

|---|---|---|

| Development Cost (NRE) | High — Full RTL, physical design, verification | Moderate — Uses licensed IPs and reference subsystems |

| Licensing Cost | Low — Mostly in-house logic | High — Paid IP cores (CPU, GPU, I/O, etc.) |

| Time to Market | Long — Custom design and verification cycle | Shorter — Integration-focused, often platform-based |

| Performance Tuning | High — Full control over timing and layout | Limited — IP black-box behavior restricts optimization |

| Verification Load | Focused — Single-purpose, scoped verification | Heavy — Complex IP interactions and corner cases |

| Risk of Re-spin | High — Full custom logic, harder to catch bugs | Medium — IP is usually well-tested but integration is risky |

| Volume Suitability | High — Payback improves with high units | Good — Better for mid-volume or evolving product lines |

| Design Reuse | Low — Hard to adapt without major rework | High — Easier to reuse across multiple designs |

| Team Skill Requirement | Advanced — Needs strong physical + logic team | Mixed — Strong integration and system-level thinking |

| Tooling/EDA Dependency | Heavy — Full flow needed (RTL to GDSII) | Shared — Platform vendors often provide part of toolchain |

Many teams attempt to strike a balance between the two, utilizing ASIC methodology for the core logic and incorporating SoC-style IP blocks around it. The key is not just choosing a design model but also knowing what your team can realistically deliver, verify, and provide production support for. Cost, time, and risk are always connected, improving one usually stresses the others.

Post-Moore Constraints Are Changing The Game

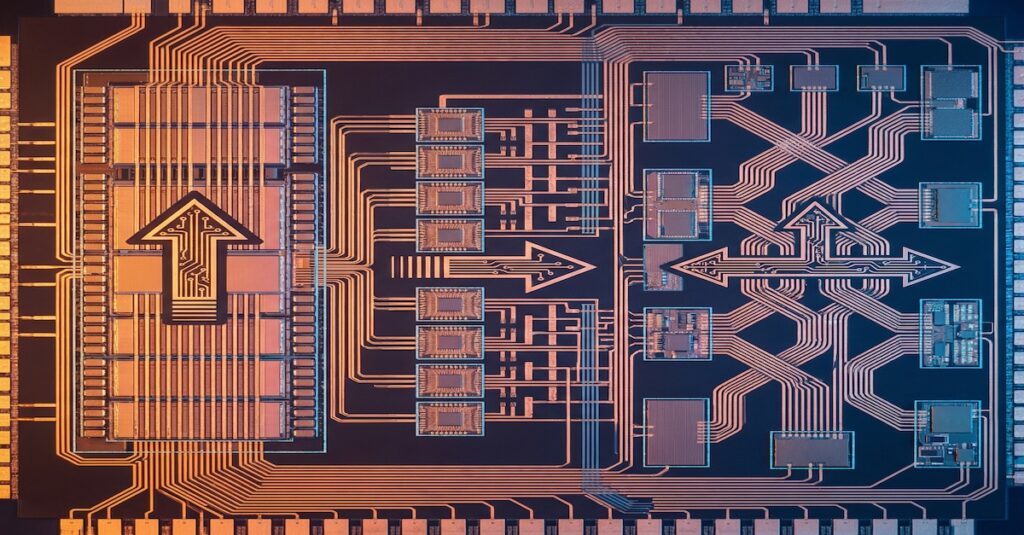

Shrinking nodes no longer guarantee better power, area, or speed. At 5nm and below, power density, interconnect delay, and thermal issues dominate. Routing is more challenging, and physical limits, such as variation and IR drop, can hinder performance gains.

For ASICs, even finely tuned blocks now face yield and manufacturability challenges. Full-custom is harder to justify unless volumes are high. Teams increasingly rely on hardened IPs and foundry-guided flows to stay within constraints.

SoCs handle this better through the reuse of mature IP blocks, stable interconnects, and known thermal profiles, thereby reducing risk. However, flexibility is limited. You cannot continually optimize data paths or packaging to fit specific system needs.

In the post-Moore era, design is now more about managing limits than pushing specs. What matters is not what performs best in theory but what yields, scales, and ships reliably.

Choose What You Can Sustain, Not Just What You Can Build

The ASIC vs SoC decision is less about architecture and more about lifecycle cost, verification effort, and team maturity. If your design requires tight control over timing, power, or area and you have the resources to manage full RTL ownership, physical implementation, and signoff, ASIC can make sense.

But every decision is expensive to change. One late bug or corner-case miss can delay the tape out or force a re-spin.

SoCs reduce that risk by leveraging proven IP and platform integration. You trade off flexibility for predictability. But even that path demands strong system validation skills, especially when IP vendors vary in quality, methodology, and update cadence.

The fundamental constraint is not what you can design, but rather what you can verify, debug, yield, and support under actual time and budget pressure. In a post-Moore landscape defined by complexity, cost, and uncertainty, sustainable execution beats architectural ambition. Choose accordingly.