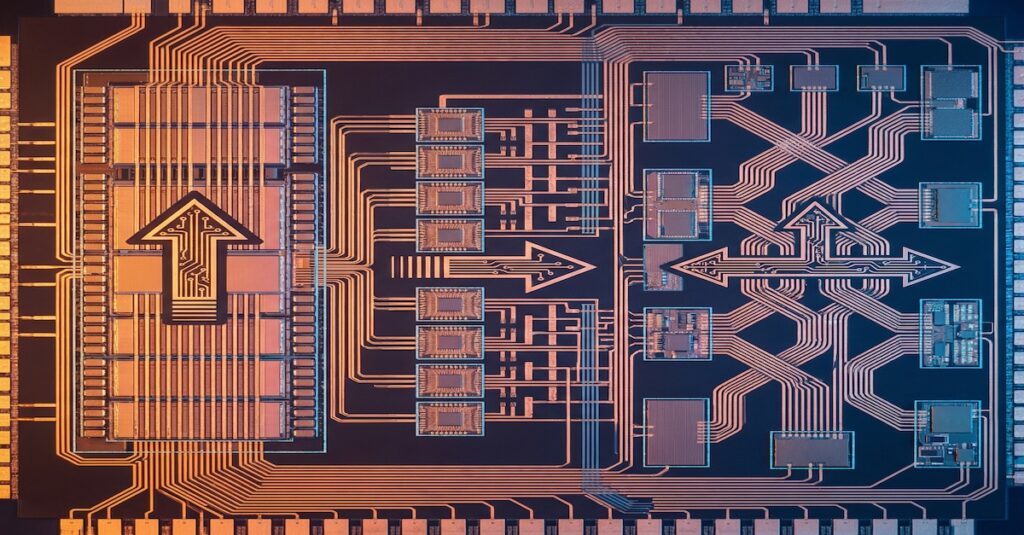

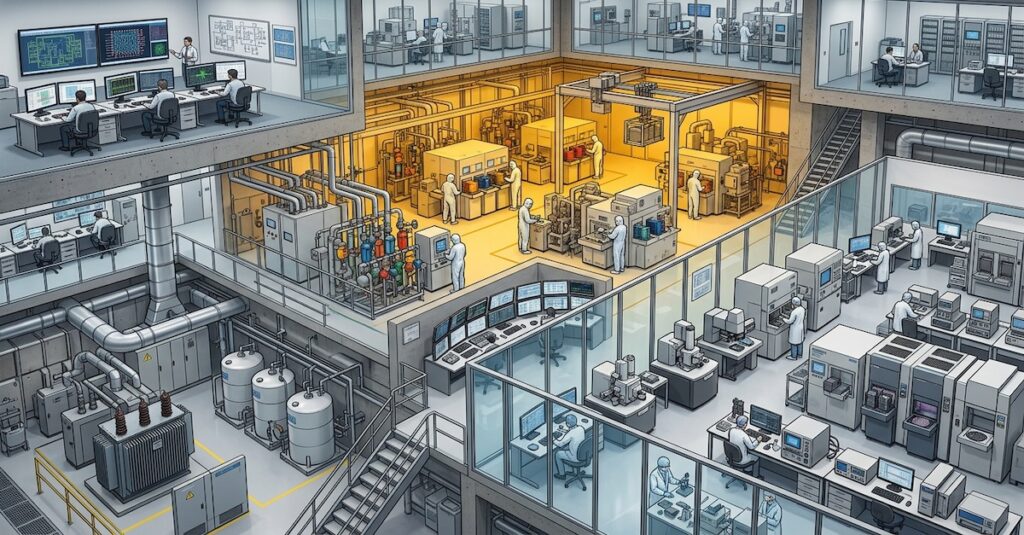

Image Generated Using DALL·E

Large Language Models (LLMs) are rapidly reshaping industries, and semiconductors are no exception. From generating RTL code and optimizing verification scripts to guiding recipe tuning in fabs, these models promise efficiency and scale. Yet the adoption of LLMs comes with risks and costs that semiconductor leaders cannot ignore.

The challenge lies not only in financial and energy investment but also in the trustworthiness, security, and long-term viability of integrating LLMs into sensitive design and manufacturing workflows.

Let us explore in more detail.

Energy And Infrastructure Burden

The deployment of large language models (LLMs) in semiconductor design and manufacturing carries a hidden but formidable cost: energy. Unlike software tools of the past, modern AI requires enormous computational resources not just for training but also for inference, verification, and ongoing fine-tuning.

For a sector already grappling with the massive electricity requirements of wafer fabrication, this additional burden compounds both operational and environmental pressures.

| Metric | Value(s) / Estimate | Source |

|---|---|---|

| U.S. data center electricity use (2023) | ~176 TWh annually | Marvell |

| Projected U.S. data center demand by 2028 | 6.7–12% of total U.S. electricity | Reuters / DOE report |

| Global data center demand by 2030 | ~945 TWh | IEA |

| GPU node draw during training (8× H100) | ~8.4 kW under load | arXiv 2412.08602 |

| Inference cost per short GPT-4o query | ≈0.43 Wh | arXiv 2505.09598 |

| Training GPT-3 energy | ≈1.29 GWh | CACM |

At scale, the infrastructure to support LLMs demands specialized GPU clusters, advanced cooling systems, and data center expansions. Each watt consumed by AI models is ultimately a cost borne by semiconductor companies, whether directly in on-premises deployments or indirectly through cloud services.

For leaders balancing fab energy efficiency targets with innovation needs, this creates a difficult trade-off: how much power should be diverted toward digital intelligence rather than physical manufacturing capacity?

Financial And Opportunity Costs

Deploying large language models in semiconductor workflows is not just a matter of compute cycles, it is a matter of capital allocation. The financial footprint includes infrastructure (GPU clusters, accelerators, cloud subscriptions), data pipelines, and the skilled personnel required for model training and fine-tuning. For semiconductor firms accustomed to billion-dollar fab projects and high non-recurring engineering (NRE) costs, this introduces a new category of spend that competes directly with traditional investments.

The opportunity cost is just as pressing. Every dollar devoted to AI infrastructure is a dollar not invested in EUV tools, yield enhancement, or chiplet R&D. While LLMs promise productivity gains, the strategic question remains: are they the best use of scarce capital compared to advancing process technology or expanding wafer capacity?

Semiconductor leaders must balance the lure of AI-driven acceleration against the tangible benefits of traditional engineering investments.

For firms already facing skyrocketing fab and equipment costs, the addition of LLM-related spending intensifies capital pressure. Even if AI promises faster time-to-market, the financial risk of sunk costs in rapidly evolving AI infrastructure is real, today’s models and accelerators may be obsolete within two years.

This creates a classic semiconductor dilemma: invest in transformative but volatile digital intelligence, or double down on the proven, capital-intensive path of lithography, yield engineering, and packaging. The wisest path may lie in hybrid strategies, small domain-specific LLM deployments tuned for semiconductor workflows, paired with careful capital prioritization for core manufacturing investments.

Risks To Security And Intellectual Property

For the semiconductor industry, intellectual property is the critical due to designs, RTL/netlists, process flows, and test data represent billions in sunk cost and future potential. Deploying large language models in design or manufacturing introduces new risks of leakage and misuse.

Unlike traditional deterministic EDA tools, LLMs are probabilistic, data-hungry, and often cloud-hosted, which amplifies the chances of sensitive data escaping organizational boundaries. Threats range from external exploits like model inversion attacks to internal mishandling, such as engineers pasting proprietary code into AI assistants.

These risks demand robust safeguards. Secure on-premises deployment, sandboxing, and strict access controls are essential, while domain-specific LLMs trained on sanitized datasets can help mitigate exposure.

Yet even with precautions, the cost of compromise far exceeds the cost of deployment, a single leak could enable cloning, counterfeiting, or billions in lost market share. For semiconductor leaders, protecting IP is not optional; it is the deciding factor in whether LLM adoption becomes a strategic advantage or an existential liability.

Accuracy, Verification, And Yield Trade-Offs

Even with all the progress, large language models generate probabilistic outputs. While this creativity can accelerate design-space exploration, it also introduces a margin of error that semiconductor companies cannot afford to overlook.

An extra semicolon in Verilog or a misplaced timing constraint can propagate downstream into silicon, leading to costly respins or yield loss. What looks like a small error in code generation can become a multimillion-dollar problem once wafers hit production.

| Risk Area | Example Impact | Source |

|---|---|---|

| Syntax & logic errors in RTL | Verilog/VHDL generated by LLMs often fails to compile or simulate correctly | arXiv 2405.07061 |

| False confidence | LLMs present flawed outputs as authoritative, increasing human trust risk | arXiv 2509.08912 |

| Verification overhead | Teams must re-run regressions and formal checks on AI-assisted designs | Semiconductor Engineering |

| Manufacturing recipe risks | Poorly validated AI-generated etch or deposition recipes can reduce yield | arXiv 2505.16060 |

| System-level propagation | Small design errors can scale into functional failures post-fabrication | IEEE TCAD |

The real challenge is that LLMs often present outputs with high confidence, even when incorrect. This shifts the burden back to verification engineers, who must re-validate LLM suggestions with rigorous simulation, formal methods, and regression testing.

Instead of eliminating work, AI may simply reshuffle it, saving time in one step but adding effort in another. For fabs, unverified LLM-driven recipe suggestions can degrade wafer yield, reduce tool uptime, or increase defect density, eroding the efficiency gains that motivated deployment in the first place.

In all, the semiconductor industry stands at a crossroads in its relationship with large language models.

On one hand, LLMs hold an undeniable promise: faster design iteration, automated verification assistance, smarter recipe generation, and a more agile workforce. On the other hand, the risks, escalating energy demands, high financial and opportunity costs, exposure of critical IP, accuracy concerns, and rapid technology obsolescence, are too significant to ignore.

The path forward is not wholesale adoption or outright rejection but disciplined integration. Companies that deploy LLMs selectively, with strong guardrails and domain-specific tailoring, will be able to capture meaningful gains without exposing themselves to catastrophic setbacks.

Those who chase scale blindly risk turning productivity tools into liability multipliers. In an industry where the margin for error is measured in nanometers and billions of dollars, the winners will be those who treat LLMs not as shortcuts, but as carefully managed instruments in the larger semiconductor innovation toolkit.