Image Generated Using DALL·E

Semiconductor And Theft

The global semiconductor industry is under growing pressure, not only to innovate, but to protect what it builds long before a chip ever reaches the fab. As the design-to-manufacture lifecycle becomes increasingly cloud-based, collaborative, and globalized, a critical vulnerability has emerged: the theft of pre-silicon design data.

This threat does not target hardware at rest or devices in the field. Instead, it targets the foundational design assets: RTL code, netlists, and layout files. It defines the behavior, structure, and physical manifestation of chips. These assets are being stolen through insider leaks, compromised EDA environments, and adversarial operations. The result is a growing ecosystem of unauthorized design reuse, counterfeit chip production, and compromised supply chains.

The implications are severe. This is not just a technical concern or a matter of intellectual property (IP) rights, it is a trillion-dollar global risk affecting innovation pipelines, market leadership, and national security.

The Threat Landscape

The theft of semiconductor design data is not a hypothetical risk, it is a growing reality. As chip design workflows become more complex, distributed, and cloud-dependent, the number of ways in which sensitive files can be stolen has expanded significantly.

| Threat Source | Description | Risk to Design Data |

|---|---|---|

| Compromised EDA Tools and Cloud Environments | Cloud-based electronic design automation (EDA) tools are widely used in modern workflows. Misconfigured access, insecure APIs, or shared environments can allow attackers to access design files. | Unauthorized access to RTL, test benches, or GDSII files due to cloud mismanagement or vulnerabilities. |

| Unauthorized IP Reuse by Partners | Third-party design vendors or service providers may retain or reuse IP without consent, especially in multi-client environments. Weak contracts and missing protections increase exposure. | Loss of control over proprietary designs; IP may be reused or sold without permission. |

| Adversarial State-Sponsored Operations | Nation-states target semiconductor firms to steal design IP and accelerate domestic chip capabilities. Several public cases have linked these efforts to cyberespionage campaigns. | Targeted theft of RTL, verification flows, and tapeout files through cyberattacks or compromised endpoints. |

| Risk at the Foundry | External foundries receive full GDSII files for fabrication. In low-trust environments, designs may be copied, retained, or used for unauthorized production. | Fabrication of unauthorized chips, IP leakage, and loss of visibility once design leaves originator’s control. |

Pre-silicon design assets like RTL, netlists, and GDSII files pass through multiple hands across internal teams, external partners, and offshore facilities. Without strong protections, these files are exposed to theft at multiple points in the workflow.

Economic And Strategic Impact

The theft of semiconductor design data results in direct financial losses and long-term strategic setbacks for chipmakers, IP vendors, and national economies. When RTL, netlists, or layout files are stolen, the original developer loses both the cost of creation and the competitive advantage the design provides. Unlike other forms of cyber risk, the consequences here are irreversible. Once leaked, design IP can be used, cloned, or altered without detection or control.

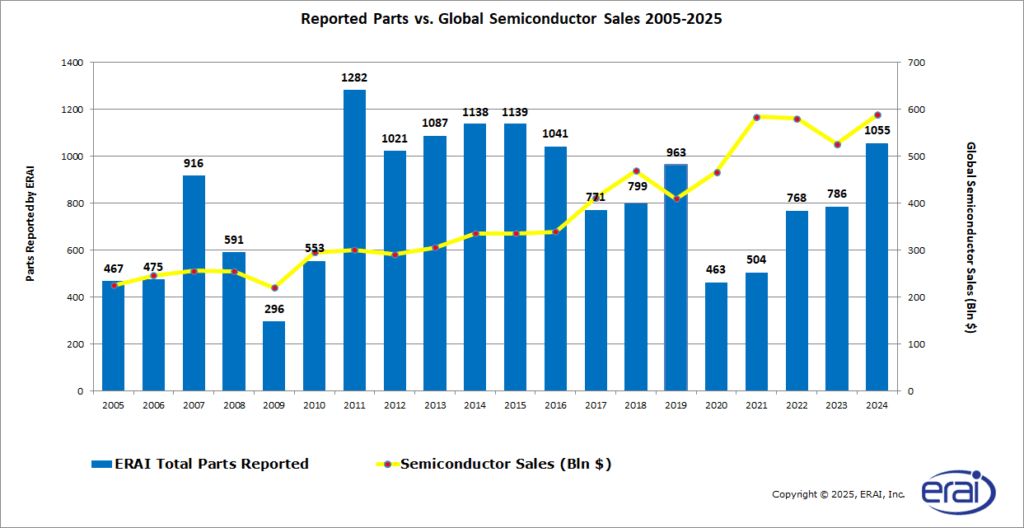

Estimates from industry and government reports indicate that intellectual property theft costs the U.S. economy up to $600 billion per year. A significant portion of this comes from high-tech sectors, including semiconductors. With global chip revenues projected to reach $1.1 trillion by 2030, even a 10 percent exposure to IP leakage, replication, or counterfeiting could mean more than $100 billion in annual losses. These losses include not only development costs but also future market position, licensing revenue, and ecosystem trust.

Key Impact Areas:

- Lost R&D Investment: High-value chip designs require years of engineering and investment. Once stolen, the original developer has no way to recover sunk costs.

- Market Erosion: Stolen designs can be used to build similar or identical products, often sold at lower prices and without legitimate overhead, reducing profitability for the originator.

- Counterfeit Integration: Stolen layouts can be used to produce unauthorized chips that enter the supply chain and end up in commercial or defense systems.

- Supply Chain Risk: When stolen designs are used to produce unverified hardware, it becomes difficult to validate the origin and integrity of chips in critical systems.

- Loss of Licensing Revenue: Third-party IP vendors lose control of their blocks, and future royalties become unenforceable when reuse happens through stolen design files.

Governments investing in semiconductor R&D also face consequences. Stolen IP undermines public investments, distorts global market competition, and creates dependencies on compromised or cloned products. When this happens repeatedly, it shifts the balance of technological power toward adversaries, weakening both commercial leadership and national security readiness.

Beyond direct monetary impact, the strategic risk is amplified when stolen IP is modified or weaponized. Malicious actors can insert logic changes, backdoors, or stealth functionality during or after cloning the design. Once deployed, compromised silicon becomes extremely difficult to detect through standard testing or field validation.

Global Implications

The theft of semiconductor design data is no longer a company-level problem. It has become a national and geopolitical issue that affects how countries compete, collaborate, and secure their digital infrastructure.

As nations invest heavily in semiconductor self-reliance, particularly through policies like the U.S. CHIPS Act or the EU Chips Act, stolen design IP can negate those investments by giving adversaries access to equivalent capabilities without the associated R&D cost or time. This reduces the effectiveness of subsidies and weakens the strategic intent behind public funding programs.

At the same time, countries that rely on foreign foundries, offshore design services, or cloud-hosted EDA platforms remain exposed. Pre-silicon IP often flows through international partners, third-party IP vendors, and subcontracted teams, many of which operate in jurisdictions with limited IP enforcement or are vulnerable to nation-state targeting.

If compromised designs are used to manufacture chips, the resulting products may be integrated into defense systems, critical infrastructure, or export technologies. This creates a long-term dependency on supply chains that cannot be fully trusted, even when fabrication capacity appears secure.

Path Forward

Securing semiconductor design data requires a shift in how the industry treats pre-silicon IP. Rather than viewing RTL, netlists, and layout files as engineering artifacts, they must be recognized as high-value assets that demand the same level of protection as physical chips or firmware. Security needs to be built into design workflows from the beginning, not added later.

This includes encrypting design files, limiting access through role-based controls, and ensuring that every handoff, whether to a cloud platform, verification partner, or foundry, is traceable and auditable.

To reduce systemic risk, companies must adopt stronger controls across the design chain and align with emerging standards. Without widespread adoption, the risk of IP leakage, unauthorized reuse, and counterfeit production will persist. The next phase of semiconductor security must begin before manufacturing ever starts, and with a clear focus on protecting design data at every stage.