Exploration of Memory and Cluster Modes in Directory-Based Many-Core CMPs.

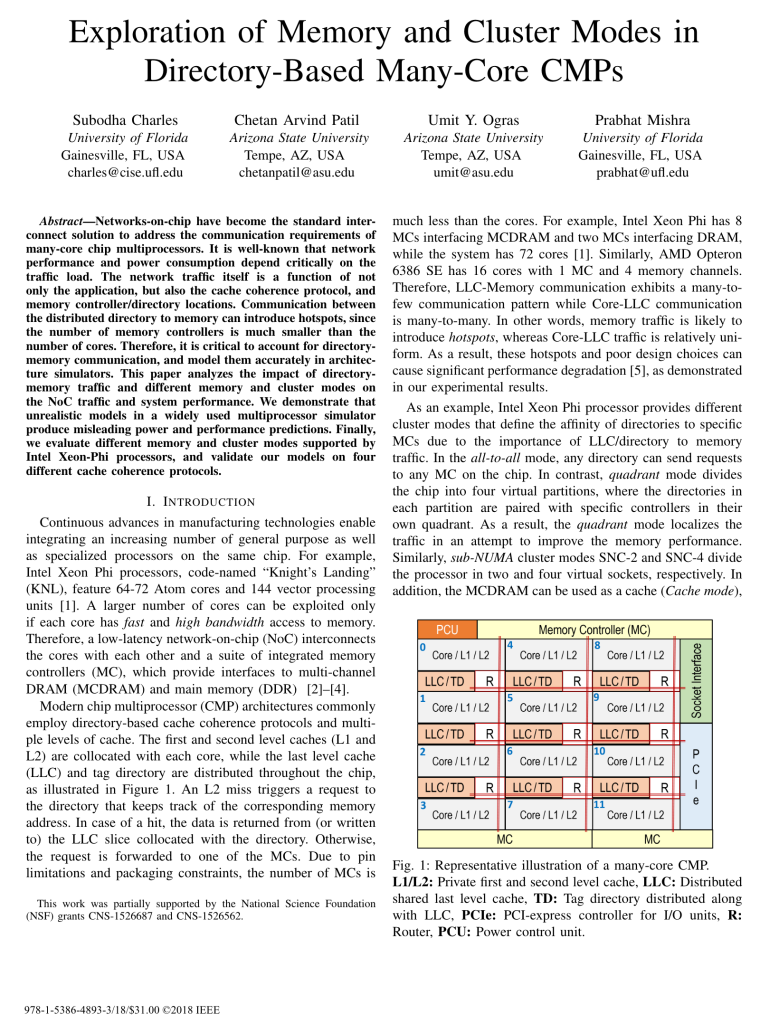

Networks-on-chip have become the standard interconnect solution to address the communication requirements of many-core chip multiprocessors. It is well-known that network performance and power consumption depend critically on the traffic load. The network traffic itself is a function of not only the application, but also the cache coherence protocol, and memory controller/directory locations. Communication between the distributed directory to memory can introduce hotspots, since the number of memory controllers is much smaller than the number of cores. Therefore, it is critical to account for directory memory communication, and model them accurately in architecture simulators. This paper analyzes the impact of directory memory traffic and different memory and cluster modes on the NoC traffic and system performance. We demonstrate that unrealistic models in a widely used multiprocessor simulator produce misleading power […]

Exploration of Memory and Cluster Modes in Directory-Based Many-Core CMPs. Read More »