# Key Components of Modern ATE Testing Environments

[epdtonthenet.net/article/219929/Key-Components-of-Modern-ATE-Testing-Environments.aspx](http://epdtonthenet.net/article/219929/Key-Components-of-Modern-ATE-Testing-Environments.aspx)

## News

Author : Chetan Arvind Patil - Contributing Writer, EPDT

20 January 2026

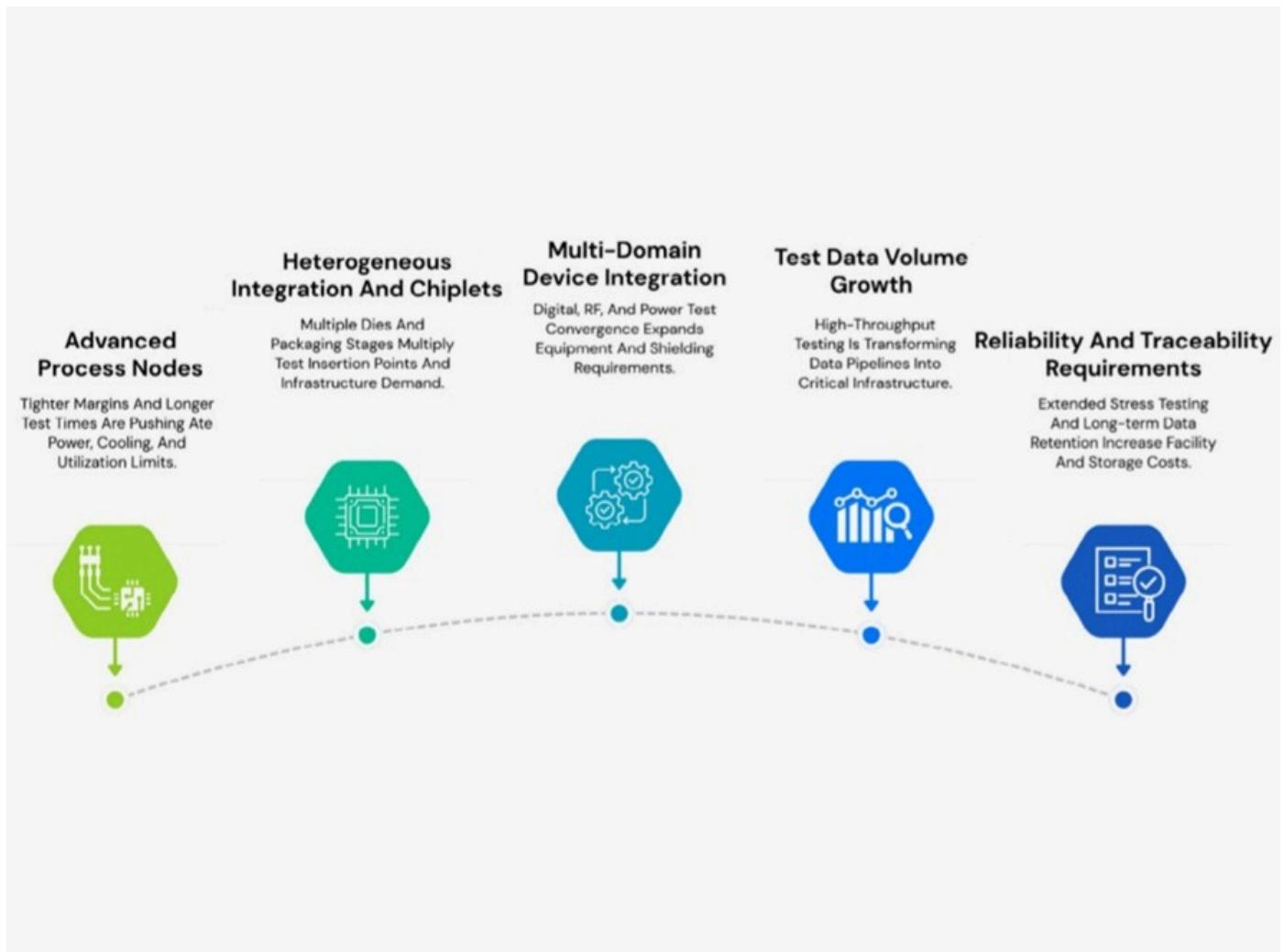

### Advanced Process Nodes

Tighter Margins And Longer Test Times Are Pushing Ate Power, Cooling, And Utilization Limits.

### Heterogeneous Integration And Chiplets

Multiple Dies And Packaging Stages Multiply Test Insertion Points And Infrastructure Demand.

### Multi-Domain Device Integration

Digital, RF, And Power Test Convergence Expands Equipment And Shielding Requirements.

### Test Data Volume Growth

High-Throughput Testing Is Transforming Data Pipelines Into Critical Infrastructure.

### Reliability And Traceability Requirements

Extended Stress Testing And Long-term Data Retention Increase Facility And Storage Costs.

Figure 1: Factors affecting ATE activities

**A modern automated test equipment (ATE) testing environment is an integrated system, rather than a single piece of equipment. While the tester remains central, effective semiconductor testing depends on a broader ecosystem of electrical, mechanical, thermal and data systems - working together in a controlled, repeatable manner.**

---

Device handling, environmental stability, measurement accuracy and reliable data movement all directly influence test quality and throughput.

As device complexity has increased and test coverage expanded across multiple domains, ATE environments have evolved from isolated test stations into system-level platforms that must deliver consistent performance at scale. In practical terms, they will include the tester, device interface hardware, material-handling systems, measurement and calibration equipment, thermal control units, plus supporting facility and data infrastructure. Load boards, probe cards, sockets and contactors provide the electrical interface, while handlers or probers enable repeatable mechanical positioning at the required throughput. Supporting systems (temperature-forcing units, calibration instruments and reliability ovens) maintain measurement accuracy across operating conditions. These elements are tightly linked to facility resources, including [power](#) distribution, cooling capacity, compressed dry air, vacuum, electro-static discharge (ESD) protection and vibration control - all of which directly affect test stability and yield.

Engineering validation laboratories and production test floors rely on many of the same components, but are designed with different objectives. Engineering labs prioritise flexibility, debug visibility and characterisation depth, typically supporting lower volumes with frequent configuration changes and extensive instrumentation. Infrastructure in these environments is optimised for precision and adaptability rather than sustained utilisation. Production test floors, by contrast, are built for standardised, high-volume execution, with tightly controlled configurations and infrastructure engineered for continuous operation, high utilisation and predictable throughput.

As silicon architectures and test requirements continue to evolve, maintaining the balance between flexibility, scale and cost has become increasingly difficult. Growing data volumes, tighter margins and additional test insertion points place new demands on both engineering and production environments, setting the stage for a closer examination of the drivers behind increasing complexity and cost in ATE-based semiconductor testing.

#### Rising complexity and expense

ATE-based semiconductor testing has become more complex as devices integrate greater functionality within increasingly tight electrical, thermal and timing margins. Advanced process nodes require higher test precision, longer test times and increased parallelism to maintain throughput, while heterogeneous integration and chiplet-based architectures add new test insertion points across the manufacturing flow. Where testing once focused mainly on digital logic,

modern devices now combine high-speed interfaces, RF, [power](#) management, sensors and embedded memory within a single package. This multi-domain integration expands test coverage and depth, placing greater demands on ATE equipment.

Market-driven requirements further intensify this challenge. Automotive, data centre and [AI](#) applications require broader coverage, longer-term traceability and greater data retention. Consequently, test flows involve wider temperature ranges, more operating corners and larger data volumes - driving the need for higher [power](#) density, tighter thermal control, better data handling, etc.

Beyond the test program itself, infrastructure scaling has become a major contributor to rising test costs. Expanding test capability is rarely limited to upgrading the ATE and often requires additional investment in [power](#) distribution, cooling capacity, floor space and environmental controls. Handlers, probers and thermal systems add continuous mechanical and energy loads, while increasing site counts further compound facility complexity. These infrastructure elements do not scale linearly, with relatively small increases in test coverage or parallelism causing disproportionately higher capital and operating costs.

| Drivers                                        | Impact on Test Complexity                                  | Infrastructure Cost Implications                               |

|------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|

| <b>Advanced process nodes.</b>                 | Increased vector count, tighter margins, longer test time. | Higher power and cooling capacity, longer tester occupancy.    |

| <b>Heterogeneous integration and chiplets.</b> | Multiple test stages and insertion points.                 | Additional handlers, probers and duplicated test cells.        |

| <b>Multi-domain device integration</b>         | Concurrent digital, RF and power testing.                  | Expanded instrumentation, shielding and isolation.             |

| <b>High-speed interfaces.</b>                  | Signal integrity sensitivity and calibration overhead.     | Improved cabling, controlled impedance and EMI mitigation.     |

| <b>Reliability and qualification standards</b> | Extended stress, corner and aging tests.                   | Larger thermal systems, reliability labs and floor space.      |

| <b>Wide operating temperature ranges.</b>      | Increased thermal cycling and soak times.                  | Higher HVAC capacity and thermal forcing equipment.            |

| <b>Parallel and multi-site testing.</b>        | Complex synchronisation and resource sharing.              | Increased power density and localised cooling.                 |

| <b>Test time optimisation pressure.</b>        | Higher tester utilisation targets.                         | Infrastructure sized for peak, not average, loads.             |

| <b>Test data volume growth.</b>                | High-frequency data capture and retention.                 | Expanded storage, networking and compute infrastructure.       |

| <b>Data traceability requirements.</b>         | Device-level genealogy and auditability.                   | Long-term data retention and secure storage systems.           |

| <b>Security and IP protection needs.</b>       | Controlled access and data isolation.                      | Secure networks, firewalls and access control systems.         |

| <b>Shorter product lifecycles.</b>             | Rapid test program changes and requalification.            | Reconfigurable infrastructure and higher engineering overhead. |

Table 1: The drivers influencing ATE complexity and expense

Test data growth introduces a parallel, often underestimated, cost trajectory. High-throughput ATE systems generate large data volumes that must be transported, processed, stored and secured. Network bandwidth, local compute resources and long-term data retention have become integral parts of the test environment. As test complexity continues to rise, efficient infrastructure management is now as critical to test economics as selection of the ATE platform itself.

Infrastructure-level approaches to mitigating cost/complexity

As ATE environments grow in capability, controlling cost and complexity requires treating infrastructure as a primary engineering discipline, not just a downstream support function. In many test organisations, infrastructure decisions around [power](#), cooling, data and floor space have historically followed tester deployment. They expand incrementally to meet immediate needs. This reactive model obscures the true cost impact of infrastructure and limits efficient scaling as environments become larger and more heterogeneous. This approach may be workable at a small scale. However, it becomes increasingly inefficient in advanced test floors. At leading nodes, facility [power](#) density, cooling capacity and data infrastructure account for a substantial share of total test ownership costs. Without coordinated planning across these domains, small increases in test capability can trigger disproportionate capital and operational expenses. To address cost and complexity, organisations need to plan their infrastructure early in test strategy lifecycles.

Effective mitigation begins at the test cell and facility level. Standardised test cells with predefined [power](#), cooling, data and mechanical interfaces reduce redesign effort. They enable reuse across products and nodes. Shared infrastructure resources, like centralised thermal systems, calibration areas and pooled compute capacity, improve utilisation and reduce overprovisioning. These choices help test floors' scale capacity without continuously expanding physical and energy footprints. Data and compute infrastructure must be optimised with the same intent. Performing basic data processing near the tester reduces network load and latency. Centralised analytics platforms support longer-term correlation and yield learning. Aligning data retention policies with actual product, customer and regulatory requirements further limits unnecessary infrastructure growth. These infrastructure-focused approaches help organisations manage rising complexity while keeping costs down.

### Infrastructure considerations for next-generation semiconductor testing

Next-generation semiconductor testing will place greater emphasis on infrastructure adaptability. Device architectures, packaging strategies and market requirements continue to evolve. Chiplet-based designs and heterogeneous integration are breaking traditional test flows into multiple insertion points at wafer, package and system levels. Test environments must now support a wider range of device form factors, thermal conditions and throughput profiles. This must happen without repeated redesign of infrastructure. Facilities optimised for narrow test configurations are likely to face higher retrofit costs and slower response to change.

At the same time, test flows are becoming increasingly data-centric. Rising data volumes and tighter coupling between testing and analytics push compute and storage resources closer to the tester. This reduces latency and unnecessary data movement. Near-tester and edge compute support faster feedback and adaptive test strategies. Centralised platforms remain essential for long-term analytics and cross-product correlation. Balancing local and centralised infrastructure will be key to maintaining scalability and cost efficiency. Security and data governance are also emerging as core infrastructure requirements. Sensitive product data now moves across distributed manufacturing ecosystems. Test environments must enforce access control, data

isolation and secure data exchange by design. Network segmentation, authenticated access and secure collaboration mechanisms between IDMs, foundries and ATMP partners will be necessary to protect product integrity and IP.

Ultimately, future test environments will require modular, scalable infrastructure strategies. Strategies should be aligned with long-term test objectives, rather than short-term capacity needs. Integrating infrastructure planning early into test strategy development will help organisations absorb rising complexity and curb the associated costs.

|

[Read More Articles](#)

### [ICsense Makes Major Investments to Boost Test Throughput](#)

(21/01/2026)

## **Fourreau Confirmed as New Alliance Electronics Chairman**

---

(19/01/2026)

## MEK Ready for Appearance at Southern Manufacturing 2026

(15/01/2026)

## [CONFIDEE Names New Recruits](#)

---

(10/01/2026)

## [Cleanova Announces 2 Significant Acquisitions](#)

---

(09/01/2026)

## [Altus Bolsters its Aftersales Support Capabilities](#)

---

(28/12/2025)

## [SolderKing Confirms Presence at Southern Manufacturing & Electronics](#)

(22/12/2025)

## [AI Platform Enables Realisation of Secure, Connected & Transparent Supply Chain Services](#)

(18/12/2025)

**SOUTHERN**

**26** Manufacturing

& Electronics

Stand J80

## Altus Prepares for Southern Manufacturing & Electronics 2026

(16/12/2025)

Editors Pick

## Breakthrough in Silicon-Integrated QCL Technology

---

## [A.R.T. Sets Out Plans for Southern Manufacturing & Electronics 2026](#)

---

## Kids Invent Stuff Gets Permanent Exhibition Space

---

## Closing the Skills Gap: What Manufacturers Need to Do

---

## Dual-Channel Digital Isolators

---

## 15.6" Format Capacitive Touch Panel

## 100V-Rated Rectifier Modules Supplied in SOT-227 Packaging

## 600V-Rated Gate Driver ICs

---

## Items of COM Hardware Based on Intel Core Ultra Series 3 Technology

---