[CONTACT \(/CONTACT.ASPX\)](#)[SUBSCRIBE \(/REGISTER/\)](#)[in](#)[\(https://www.linkedin.com/in/EPDTNEWS/\)](https://www.linkedin.com/in/EPDTNEWS/)product-

design-[test-](#)<https://twitter.com/EPDTNEWS>[\(/index.aspx\)](#)**TOSHIBA****Empowering Motion**Motor Control Solutions

Brushed, Brushless, Stepper[\(https://toshiba.semicon-storage.com/eu/semiconductor/knowledge/highlighted-contents/articles/journey-of-motor-control.html\)](https://toshiba.semicon-storage.com/eu/semiconductor/knowledge/highlighted-contents/articles/journey-of-motor-control.html)**NEWS (..../NEWS.ASPX)****FEATURES (..../FEATURES.ASPX)****PRODUCTS (..../PRODUCTS.ASPX)****VIDEOS (..../VIDEOS.ASPX)****BLOGS (..../BLOGS.ASPX)****TEST (..../TEST.ASPX)****OUTSOURCING (..../ELECTRONICS-OUTSOURCING.ASPX)****DISTRIBUTION (..../DISTRIBUTION.ASPX)****STEM (..../STEM.ASPX)****ABOUT US**[News \(..../features/212/News/\)](#)

## The Engineering Hurdles Behind ATE Test Programs for Semiconductor Product Development

19 July 2025

Author : Chetan Arvind Patil - Contributing Writer, EPDT

Figure 1: Key steps in developing ATE test programs

**Semiconductor devices must satisfy stringent requirements for performance, reliability and safety before being delivered to customers. Although design simulations verify circuit behaviour, manufacturing introduces variability, defects and physical stresses that simulations alone cannot fully anticipate.**

To address these gaps, silicon testing plays a crucial role, detecting faults and ensuring devices operate within specified limits under real-world conditions. Without thorough testing, defective chips could enter production, potentially causing system failures, costly recalls, customer dissatisfaction, plus significant financial/reputational damage.

So as to minimise such risks, semiconductor manufacturers rely on a structured series of test stages – each designed to detect different types of defects throughout production processes. A wafer probe examines individual dies on the wafer to identify/discard defective units before they are packaged. Further tests then evaluate packaged devices under varied temperatures and voltages to detect issues introduced during assembly or packaging. System-level test (SLT) procedures subject devices to workloads similar to real applications, revealing failures that may have been hidden from earlier tests.

Executing these test stages requires more than just equipment. It depends on carefully designed systems and procedures. These must consistently detect defects, verify performance and operate efficiently to meet high-volume demands and fast timelines.

At the core of such capabilities will be the way automated test equipment (ATE) is configured to evaluate each specific semiconductor device, both during wafer-level testing and the subsequent testing of packaged parts. Dedicated test programs transform detailed device specifications into precise testing routines executed on sophisticated hardware platforms. Given their fundamental role in upholding semiconductor quality and

manufacturing efficiency, understanding what ATE test programs are, the complexity behind their development and the engineering challenges involved will be paramount.

### What is an ATE test program?

An ATE test program is a software application that instructs test instrumentation on how to verify whether a semiconductor device meets its electrical and functional specifications. It turns general-purpose test hardware into a dedicated system tailored for evaluating a specific device or product family, making certain that each test set-up is precisely matched to the requirements of the device-under-test (DUT).

A typical ATE test program performs a wide range of measurements and checks to validate device performance across all critical parameters. These include:

- Contact tests - Which confirm that all device pins are correctly connected and free of unintended shorts or open circuits.

- DC parametric tests - For measuring static electrical parameters (such as voltages, currents, leakage levels and threshold voltages) to ensure device operation within specified limits.

| Complexity Factor                      | Ways To Mitigate                                                                                             |                                                                                                                       |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Device Functionality Diversity         | Partitioning tests, using design-for-test (DFT) features, coordinating digital, analogue and RF instruments. | - Functional and logic tests                                                                                          |

| Advanced Packaging                     | Indirect measurements, custom probe cards, built-in test circuits for inaccessible paths.                    | - Where digital patterns or analogue signals are applied to exercise a device's logic circuits and functional blocks, |

| High-Speed Operation                   | Precision load board design, timing calibration, managing signal integrity for fast interfaces.              | verifying that all intended operations execute correctly.                                                             |

| Multi-Site Testing                     | Balanced power delivery, synchronised timing, robust load boards for parallel devices.                       | - AC timing tests                                                                                                     |

| Calibration and Measurement            | Regular calibration, compensating for parasitics, correlating results across testers and sites.              | - To evaluate dynamic                                                                                                 |

| Software Complexity                    | Reusable test IP, integration with simulation tools, adaptive testing logic.                                 |                                                                                                                       |

| Debug and Evolving Specs               | Collaboration with design teams, flexible test code, thorough root-cause analysis.                           |                                                                                                                       |

| Power and Thermal Constraints          | Managing high current, thermal monitoring, safe operating limits in test flows.                              |                                                                                                                       |

| Yield Optimisation and Economics       | Data-driven test trimming, statistical analysis, balancing coverage with cost/unit.                          |                                                                                                                       |

| Integration with Manufacturing Systems | Seamless data handling, traceability, compatibility with factory automation tools.                           |                                                                                                                       |

Table 1: Mitigating device complexity issues

performance by measuring timing parameters (such as clock-to-output delays, set-up and hold times, propagation delays, etc.).

ATE test programs are deployed at multiple stages of semiconductor manufacturing, each serving a distinct role in ensuring product quality. During probe testing, the program tests individual dies directly on the wafer to identify and separate functional units from defective ones before packaging. The program next evaluates packaged devices under various conditions to uncover defects introduced during assembly and categorise devices into performance bins suitable for different market segments.

Ultimately, an effective ATE test program must strike a careful balance between achieving comprehensive test coverage and maintaining efficient test times. This balance is critical because, in high-volume manufacturing, any delays experienced will be costly. Optimising test program execution is therefore essential, not only for ensuring product quality, but also maintaining the overall efficiency and competitiveness of semiconductor production.

### Associated engineering challenges

Developing ATE test programs is a demanding engineering task. With modern chips integrating diverse functions, ranging from digital logic and analogue circuitry to RF blocks and high-speed interfaces, each requiring unique test

strategies and specialised instrumentation, the challenges are getting ever greater.

For example, digital testing involves high-speed pattern generation and scan diagnostics, while RF testing demands precise frequency and power measurements under low-noise conditions. Advanced packaging, including chiplets and 3D stacking, limits physical signal access, forcing engineers to rely on indirect probing, built-in monitors, or custom hardware solutions.

High-speed operation further complicates testing. Multi-GHz signals require ps timing precision and meticulous load board design to avoid signal reflections and crosstalk. Things get more difficult with multi-site testing, where numerous devices are tested simultaneously to reduce the cost/unit. Engineers must therefore ensure balanced power delivery, synchronised timing, and uniform signal integrity across all sites. The load boards themselves become complex engineering projects, demanding precise impedance control and thermal management.

### The software aspect

Software complexity adds another dimension. ATE test programs integrate instrument control, adaptive test logic and large-scale data handling. They interface with design tools to translate simulation patterns into executable test routines and must adapt dynamically during runtime to skip redundant tests or adjust measurements. Debugging is particularly challenging, as failures can stem from silicon defects, hardware issues, timing errors, or software bugs, requiring careful diagnosis across multiple layers.

To address these challenges, engineers should utilise reusable test IP, collaborate closely with design teams to incorporate DFT features and partner with ATE vendors to develop custom solutions. As technology advances into fields such as AI ([/article/212227/EPDT-Review-of-the-Year-Part-11-AI-Technology.aspx](#)) accelerators, photonics and quantum computing, ATE test program development difficulties will intensify, demanding innovative methods and more profound expertise to maintain quality and efficiency in semiconductor manufacturing.

### Cost impacts

Addressing the engineering challenges of ATE test program development calls for significant time and resource allocation. Creating a test program for an advanced system-on-chip (SoC) often requires many thousands of engineering hours (encompassing activities such as writing test vectors, coding measurements and debugging the first silicon). Furthermore, high-performance ATE systems can carry hefty price tags, with additional costs for custom hardware (load boards, probe cards, etc.). Even in high-volume manufacturing, 1s extra test time per device can result in major increases in overall production costs.

To manage these costs while maintaining quality, the industry relies on several strategies. These include DFT features built into chips that simplify external testing, thus reducing development effort and test time. Adaptive testing dynamically skips specific steps for devices that perform well in early checks, improving efficiency without sacrificing quality. Multi-site testing also remains highly effective for reducing cost/unit.

Looking ahead, advances in software tools, analytics, reusable test IP and vendor collaboration will all contribute to maintaining both the rigor and cost-effectiveness of ATE testing as new technologies emerge. Balancing these challenges with efficiency will remain vitally important for delivering high-quality semiconductor products and keeping pace with ongoing innovation.

**Figure 2: The cost and complexity of ATE test programs**

[Print this page](#) | [E-mail this page](#)

[READ MORE ARTICLES](#)

UK Circuits Joins Make UK Defence ([..../216722/UK-Circuits-Joins-Make-UK-Defence.aspx](#))

© (22/07/2025)

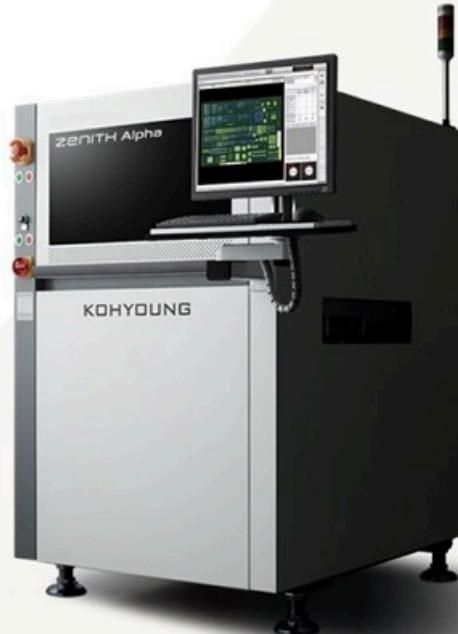

New 3D Optical Inspection Equipment Deployment (./216447/New-3D-Optical-Inspection-Equipment-Deployment.aspx)

© (03/07/2025)

Core Management Team at Axiom Bolstered ([..../216325/Core-Management-Team-at-Axiom-Bolstered.aspx](#))

© (26/06/2025)

TT Electronics' Mexican Contract Manufacturing Operation Gains Medical Certification

([..../216284/TT-Electronics--Mexican-Contract-Manufacturing-Operation-Gains-Medical-Certification.aspx](https://www.epdtonthenet.net/article/216284/TT-Electronics--Mexican-Contract-Manufacturing-Operation-Gains-Medical-Certification.aspx))

© (25/06/2025)

Altus Proves Pivotal in Kentec Electronics' Efforts to Improve Through-Hole Inspection Operation

(..../216146/Altus-Proves-Pivotal-in-Kentec-Electronics--Efforts-to-Improve-Through-Hole-

Inspection-Operation.aspx)

© (17/06/2025)

Array of Silicon Services Now Offered sureCore ([..../216120/Array-of-Silicon-Services-Now-Offered-sureCore.aspx](#))

© (16/06/2025)

Investment Certification Secured by ESCATEC's Bulgarian Operation ([..//216044/Investment-Certification-Secured-by-ESCATEC-s-Bulgarian-Operation.aspx](#))

© (11/06/2025)

## Electronics Manufacturing Services Market

Market Value

2023

USD 537.10

Billion

CAGR

2024-2031

7.3%

Market Value

2031

USD 945.67

Billion

### Key Drivers

Increasing Demand for High-Mix, Low-Volume Production Capabilities Fuels the Market Development

### Key Restraints

Complexity of Managing Multi-Tier Global Supply Chains Hampers the Market Growth

### Future Opportunities

Expansion of Services into Medical Device Manufacturing for Regulatory Compliance Creates Growth Opportunities

### Segmentation

By Service Type

By Service Provider Type

By End-User Industry

### REGIONAL ANALYSIS

#### Asia Pacific

Expected to grow with the highest CAGR growth

EMS Sector Set for Long-Term Growth Despite Continued Challenges ([..//215980/EMS-Sector-Set-for-Long-Term-Growth-Despite-Continued-Challenges.aspx](#))

© (08/06/2025)

## New Partnership for 3D AOI with FermionX

Altus Supports FermionX in Augmenting its Product Inspection Capabilities ([../215629/Altus-Supports-FermionX-in-Augmenting-its-Product-Inspection-Capabilities.aspx](#))

© (20/05/2025)

### EDITORS PICK

Optoelectronics Design Contest Begins ([../216740/Optoelectronics-Design-Contest-Begins.aspx](#))

EngineeringUK Bursaries Aimed at Helping Schools with Maximising Impact of STEM Efforts ([../216387/EngineeringUK-Bursaries-Aimed-at-Helping-Schools-with-Maximising-Impact-of-STEM-Efforts.aspx](#))

Student Hyperloop Team Benefits from Schaltbau Financial Backing ([../216344/Student-Hyperloop-Team-Benefits-from-Schaltbau-Financial-Backing.aspx](#))

Comprehensive Engineering Lab for Use in Educational Environments ([../216177/Comprehensive-Engineering-Lab-for-Use-in-Educational-Environments.aspx](#))

## POPULAR ARTICLES

SEGGER Toolchain Integrated with CMake & VS Code ([./216793/SEGGER-Toolchain-Integrated-with-CMake-VS-Code.aspx](#))

Multi-Channel Impedance Measurement ICs ([./216771/Multi-Channel-Impedance-Measurement-ICs.aspx](#))

Automotive Qualified 3D Magnetic Sensing Devices ([./216767/Automotive-Qualified-3D-Magnetic-Sensing-Devices.aspx](#))

Baseband Development Platform for OpenRAN RUs with 7.2 Functional Split ([./216765/Baseband-Development-Platform-for-OpenRAN-RUs-with-7-2-Functional-Split.aspx](#))

GaN-Based Motor Drive Reference Design for Humanoid Robots ([./216762/GaN-Based-Motor-Drive-Reference-Design-for-Humanoid-Robots.aspx](#))

Infineon PSOC™

Control C3

Microcontrollers

2 / 6

VISIT OUR WEBSITE

→

## SUBSCRIBE TO NEWSLETTER

SUBSCRIBE ([HTTPS://DATA.IMLGROUP.UK/EPDT-REG-PAGE/](https://data.imlgroup.uk/EPDT-REG-PAGE/))

([https://go2.tek.com/en-isovu-isolated-current-shunt-probes-wc/?utm\\_source=epdt&utm\\_medium=display&utm\\_campaign=brand-tek-epdtweb-en&utm\\_content=hydrabanner&utm\\_term=prospecting](https://go2.tek.com/en-isovu-isolated-current-shunt-probes-wc/?utm_source=epdt&utm_medium=display&utm_campaign=brand-tek-epdtweb-en&utm_content=hydrabanner&utm_term=prospecting))

## EPDT TV

Video Interview: Simplifying Connector/Cabling Specification Processes via Digital Tools

([.../video/216374/Video-Interview--Simplifying-Connector-Cabling-Specification-Processes-via-Digital-Tools.aspx](https://.../video/216374/Video-Interview--Simplifying-Connector-Cabling-Specification-Processes-via-Digital-Tools.aspx))

Video Interview: Overcoming Acute Constraints of Edge-Situated Connected Hardware via Emerging Wireless SoC Technology

([.../video/216362/Video-Interview--Overcoming-Acute-Constraints-of-Edge-Situated-Connected-Hardware-via-Emerging-Wireless-SoC-Technology.aspx](https://.../video/216362/Video-Interview--Overcoming-Acute-Constraints-of-Edge-Situated-Connected-Hardware-via-Emerging-Wireless-SoC-Technology.aspx))

EPDT's Big Arduino Giveaway - Enter Now!!! ([.../video/216258/EPDT-s-Big-Arduino-Giveaway-Enter-Now-.aspx](https://.../video/216258/EPDT-s-Big-Arduino-Giveaway-Enter-Now-.aspx))

## EPDT DIGITAL EDITION

(<https://edition.pagesuite.com/html5/reader/production/default.aspx?pubname=&pubid=d26bb4fe-3688-46af->

Read the latest edition (<https://edition.pagesuite.com/html5/reader/production/default.aspx?pubname=&pubid=d26bb4fe-3688-46af-9048-19cedca03881>)

---

## POPULAR ARTICLES

**Making Plans for Nigel - Test Software Suite Now Benefits for Addition of AI Functionality** ([..216737/Making-Plans-for-Nigel-Test-Software-Suite-Now-Benefits-for-Addition-of-AI-Functionality.aspx](https://216737/Making-Plans-for-Nigel-Test-Software-Suite-Now-Benefits-for-Addition-of-AI-Functionality.aspx))

**650V-Rated GaN FETs Enable Higher Density Power Conversion Implementations** ([..216476/650V-Rated-GaN-FETs-Enable-Higher-Density-Power-Conversion-Implementations.aspx](https://216476/650V-Rated-GaN-FETs-Enable-Higher-Density-Power-Conversion-Implementations.aspx))

**More Effective BLDC Motor Control in Automobiles** ([..216071/More-Effective-BLDC-Motor-Control-in-Automobiles.aspx](https://216071/More-Effective-BLDC-Motor-Control-in-Automobiles.aspx))

**Distribution Dialogues: Adding New Commercial Dimensions** ([..215962/Distribution-Dialogues--Adding-New-Commercial-Dimensions.aspx](https://215962/Distribution-Dialogues--Adding-New-Commercial-Dimensions.aspx))

[HOME](https://www.epdtonthenet.net) ([CONTACT](https://www.epdtonthenet.net/contact.aspx)) [TERMS & CONDITIONS](https://www.epdtonthenet.net/termsandconditions.aspx) ([PRIVACY](https://www.epdtonthenet.net/privacypolicy.aspx)) [COOKIES](https://www.epdtonthenet.net/cookies.aspx)

Copyright © IML Group 2025 All rights reserved