HOME MICRO MANUFACTURING METROLOGY MEMS HIGH PRECISION ARTICLES EVENTS

# Beyond Moore: Design and Manufacturing Challenges in Systemon-a-Wafer

JUNE 4, 2024 10:18 AM

Chetan Arvind Patil. Senior Product Engineer. NXP USA Inc

For decades, Moore's Law has been the guiding principle of the semiconductor industry, driving exponential growth in computing power by doubling the number of transistors on a chip approximately every two years. However, as the semiconductor chip design and manufacturing approach the physical and economic limits of traditional scaling, the industry must look beyond Moore's Law for innovative solutions. Beyond Moore: Design and Manufacturing Challenges in System-on-a-Wafer - CMM Web Portal

There have already been many solutions on this front, such as multicore chips, System-On-A-Chip (SoC), 2.5D to 3D-based SoCs, and most recently, the advent of heterogeneous integration using chipset-based solutions, an extension of System-In-A-Package (SiP).

Lately, however, one more promising solution beyond Moore's is the System-On-A-Wafer (SoW), which integrates multiple dies onto a single wafer to create an extensive, contiguous system.

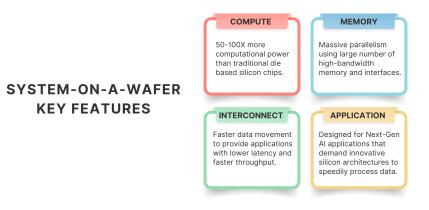

SoW not only goes beyond the limitation of silicon area but is also seen as an alternative to providing silicon chips geared towards neverbefore-seen memory and compute-intensive applications, i.e., Artificial Intelligence.

Understanding System-On-A-Wafer (SoW)

## June-2024 - 1

System-On-A-Wafer (SoW) is an advanced technology that integrates various functional dies, such as processors, memory, and specialized accelerators, onto a single wafer. Unlike traditional System-On-Chip (SoC) or System-In-Package (SiP) designs, SoW aims to create a unified, large-scale system that offers higher performance and efficiency.

One key distinction of SoW is that it typically produces a single finished silicon product per wafer, unlike SoC or other techniques that often yield multiple finished silicon products. This unique characteristic of SoW can be seen as a trade-off, as it can be more risky and costly. However, it also brings several benefits tailored to specific applications and use cases, making it a compelling choice in particular scenarios. There are several ways to visualize how SoWs get designed and then fabricated is by comparing them with traditional die-based chips, where there are numerous (depending on die size/area) die per wafer. In contrast, SoW takes one wafer to create one single die, i.e., one single chip. Also, the focus of SoW is on providing an end solution 50-100x more potent than traditional die-based chips.

| Aspect                                        | Traditional Die-Based Chip<br>Fabrication                                                                                                                                                                                | System-On-A-Wafer (SoW) Fabrication                                                                                                                                                                                                   |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integration And<br>Architecture               | <ul> <li>Discrete chips are fabricated,<br/>packaged, and assembled on a PCB.</li> <li>Modular approach allows easy<br/>upgrades or replacements.</li> </ul>                                                             | <ul> <li>Multiple dies (for the same end product)<br/>are integrated on a single wafer, functioning<br/>as a unified system.</li> <li>Complex design is required for the<br/>seamless integration of diverse components</li> </ul>    |

| Performance And<br>Latency                    | <ul> <li>Data transfer between chips occurs<br/>through external interconnects,<br/>introducing latency.</li> <li>Performance is limited by the speed<br/>and efficiency of PCB traces and<br/>interconnects.</li> </ul> | <ul> <li>Direct interconnects between dies on the<br/>wafer minimize latency and maximize<br/>throughput.</li> <li>Improved signal integrity and reduced<br/>interconnect lengths enhance performance.</li> </ul>                     |

| Manufacturing<br>Complexity                   | <ul> <li>Utilizes established semiconductor<br/>manufacturing processes.</li> <li>Each die is packaged separately,<br/>simplifying some aspects of<br/>manufacturing.</li> </ul>                                         | <ul> <li>Requires cutting-edge lithography,<br/>bonding, and etching techniques.</li> <li>The entire wafer may be packaged as one<br/>system, adding complexity to packaging.</li> </ul>                                              |

| Yield And Cost                                | <ul> <li>Defects in one die do not typically<br/>affect others, allowing for better yield<br/>management.</li> <li>Lower initial costs due to established<br/>processes.</li> </ul>                                      | <ul> <li>Defects in the wafer can affect multiple<br/>dies, leading to higher yield challenges.</li> <li>Higher initial costs due to advanced<br/>techniques and lower yields.</li> </ul>                                             |

| Power Efficiency<br>And Thermal<br>Management | <ul> <li>Separate chips generate heat<br/>independently, often requiring<br/>individual cooling solutions.</li> <li>Power distribution is managed at the<br/>PCB level.</li> </ul>                                       | <ul> <li>Integrated design allows for more efficient<br/>heat dissipation across the wafer.</li> <li>Power can be distributed more efficiently<br/>within the wafer, reducing losses.</li> </ul>                                      |

| Scalability And<br>Flexibility                | <ul> <li>Adding or upgrading components<br/>involves adding more chips to the<br/>PCB.</li> <li>High flexibility in changing or<br/>upgrading individual components.</li> </ul>                                          | <ul> <li>Scaling requires integrating more dies onto<br/>the wafer, which is limited by wafer size and<br/>yield.</li> <li>While heterogeneous integration is<br/>possible, making changes or upgrades is<br/>more complex</li> </ul> |

| Wafer Size                                    | - Can make use of 6, 8, and 12-inch<br>wafer<br>- Thus, the cost can be determined<br>based on the business case and<br>demand.                                                                                          | - By default, has to make use of a 12-inch<br>wafer to reach the break-even point<br>- Even then, the negative yield impact can<br>derail the ROI                                                                                     |

# SoW Versus GPU For Artificial Intelligence Application

Artificial Intelligence (AI) applications have already revolutionized industries by enabling advanced data processing, machine learning, and deep learning capabilities. Both System-On-A-Wafer (SoW) and Graphics Processing Units (GPUs) target this market by offering robust computational solutions. However, SoW can potentially significantly disrupt and enhance the landscape of AI silicon and the applications that use it.

**GPUs In Al:** GPUs have long been the backbone of AI and deep learning applications. Their architecture, designed for parallel processing, equips them to handle the massive computational requirements of AI workloads efficiently. GPUs shine in training deep neural networks, executing complex mathematical operations, and processing large datasets in real time. Industries from autonomous driving and healthcare to finance and entertainment heavily depend on GPUs to power their AI systems, underscoring their broad application.

**SoW In Al:** System-On-A-Wafer (SoW) technology is emerging as a compelling alternative to GPUs, especially for applications that demand unprecedented levels of integration and performance. SoW integrates multiple functional dies, including CPUs, GPUs, and specialized accelerators, directly onto a single wafer. This innovative approach offers significant benefits in terms of performance, power efficiency, and latency, making it a highly viable option for the same AI applications that are currently dominated by GPUs.

Let us take a more detailed look at different technical characteristics of how SoW will challenge GPUs:

| Aspect                      | System-On-A-Wafer (SoW)                                                                                                | Graphics Processing Unit (GPU)                                                                                                          |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                | Integrating multiple dies on a single wafer<br>creates an extensive, contiguous system.                                | Comprises multiple cores optimized for<br>parallel processing on a single die or a small<br>number of interconnected dies.              |

| Performance                 | Higher performance due to improved<br>interconnect and thermal management.                                             | High performance through massive<br>parallelism, with thousands of cores designed<br>for concurrent processing.                         |

| Scalability                 | Adding more dies to the wafer achieves<br>high scalability, but this is limited by<br>wafer size and yield management. | Scalable through multi-GPU configurations but<br>limited by inter-GPU communication overhead<br>and power constraints.                  |

| Power<br>Efficiency         | Potential for better power efficiency due<br>to optimized interconnects and thermal<br>management.                     | Generally, there is high power consumption,<br>though recent advancements focus on<br>improving efficiency for AI workloads.            |

| Latency                     | Lower latency due to shorter interconnects between dies.                                                               | It is designed to minimize latency in parallel<br>processing tasks but can introduce delays in<br>multi-GPU setups.                     |

| Cost                        | High initial cost due to advanced<br>manufacturing techniques and lower yield<br>rates.                                | Generally, there is a lower cost per unit due to<br>mature manufacturing processes, but costs<br>can add up in large-scale deployments. |

| Manufacturing<br>Complexity | Highly complex manufacturing process<br>requiring advanced lithography, etching,<br>and bonding techniques.            | Less complex compared to SoW, benefiting<br>from established fabrication processes for<br>single-die GPUs.                              |

| Flexibility                 | High flexibility in integrating<br>heterogeneous components (CPUs, GPUs,<br>specialized accelerators).                 | Limited to the architecture of the GPU, though<br>modern GPUs can include tensor cores and<br>other specialized units.                  |

| Heat<br>Dissipation         | Improved heat dissipation across the wafer surface.                                                                    | Effective heat dissipation mechanisms, but car<br>be challenged in high-density or multi-GPU<br>configurations.                         |

| Applications                | Ideal for large-scale AI applications<br>requiring vast computational resources<br>and high efficiency.                | Widely used in AI and deep learning due to<br>optimized parallel processing capabilities and<br>software support.                       |

#### June-2024 - 2

Adoption And Way Forward For SoW

Beyond Moore: Design and Manufacturing Challenges in System-on-a-Wafer - CMM Web Portal

The adoption of System-On-A-Wafer (SoW) technology in the semiconductor industry is poised to bring about a paradigm shift in how high-performance computing systems are designed and manufactured. While promising significant advantages, this transition will involve overcoming several challenges and strategically navigating the existing landscape.

One of the primary driving factors for adopting SoW is the increasing demand for enhanced computational power. AI and machine learning applications and data-intensive tasks such as big real-time data interpretation and decision-making requires unprecedented computational power. SoW technology, by integrating multiple dies on a single wafer, can more effectively meet these performance requirements than traditional chip architectures. Additionally, the proximity of very large integrated components in SoW reduces latency and increases data transfer rates, providing a significant advantage for applications requiring real-time processing and high-bandwidth communication.

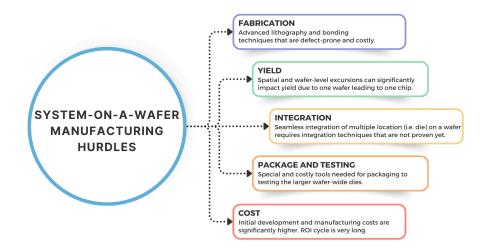

Despite its advantages, the adoption of SoW faces several challenges. Manufacturing complexity is a significant hurdle. The fabrication of SoW requires cutting-edge lithography, bonding, and etching technologies, which are more complex and costly than traditional semiconductor manufacturing processes. Yield management is another critical issue, as defects in the wafer can affect multiple integrated dies, posing significant yield challenges. Advanced defect detection and yield improvement techniques are essential to make SoW commercially viable.

Cost considerations are also significant. The initial costs of developing and manufacturing SoW are higher due to the advanced techniques required. However, economies of scale may help reduce these costs as the technology matures and scales. Significant investments in new infrastructure and equipment will also be necessary to transition from traditional manufacturing processes to SoW technology.

In the end, adopting System-On-A-Wafer (SoW) technology represents a significant opportunity for the semiconductor industry to meet the growing demands for high-performance, energy-efficient, and scalable computing solutions. While there are considerable challenges to overcome, the potential benefits of SoW in terms of performance, efficiency, and integration make it a promising technology for the

Beyond Moore: Design and Manufacturing Challenges in System-on-a-Wafer - CMM Web Portal

future. With continued innovation and collaboration across the industry, SoW has the potential to transform high-performance computing and drive the next wave of technological advancements.

JUNE 4, 2024 10:18 AM

## HOME MICRO MANUFACTURING METROLOGY MEMS HIGH PRECISION

## ARTICLES EVENTS

## TERMS & CONDITIONS PRIVACY POLICY AND COOKIES (GDPR) ABOUT CONTACT ADVERTISE

© 2024 MST Global Ltd. All rights reserved.

BUILT WITH METRO PUBLISHER™